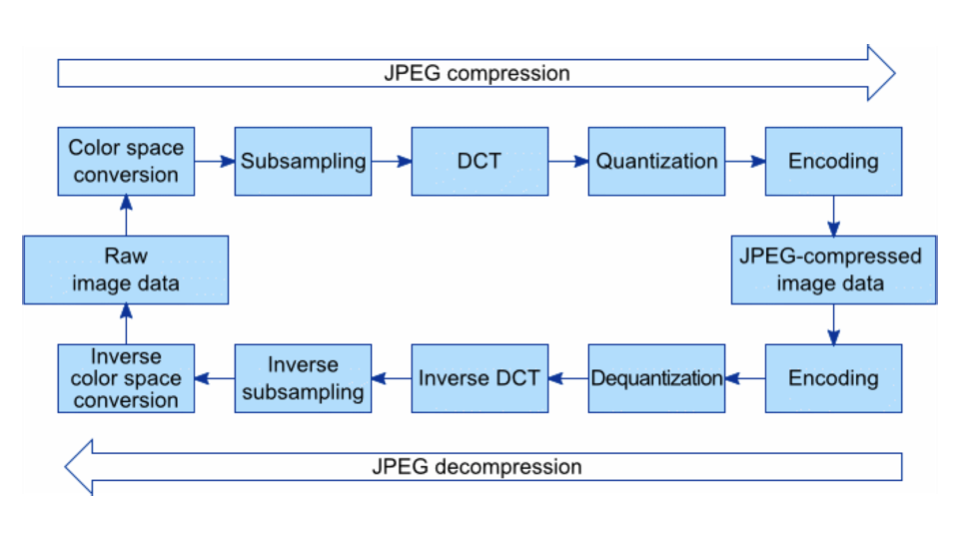

To compress and decompress an image with the help of JPEG algorithm on FPGA using Tang Primer Dev Board.

Implementing JPEG encoder algorithm with Verilog on FPGA as Phase 1. Phase 2 includes the interfacing of a camera module (preferably ov2640 or ov7670) and a TFT display.

FPGA stands for Field Programmable Gate Array.

- Download and install Tang Dynasty by following the instructions mentioned in the link above.

- Also istall the USB drivers of for Tang Primer Dev Board.

- Download and Install Modelsim.

- Clone or download the compression modules in this repo.

- Open Tang Dynasty and generate RTL file by creating project and following this process.

32x32 pixel input image and 70% compressed results